We make things visible®

Concept Engineering is the leader in electronic system visualization software, with applications in multiple industries. We help engineers debug complex semiconductor designs, accelerate automotive electronic systems development and service with responsive smart schematic rendering, and provide powerful OEM visualization engines to computer aided tool developers for their EDA & CAD product lines.

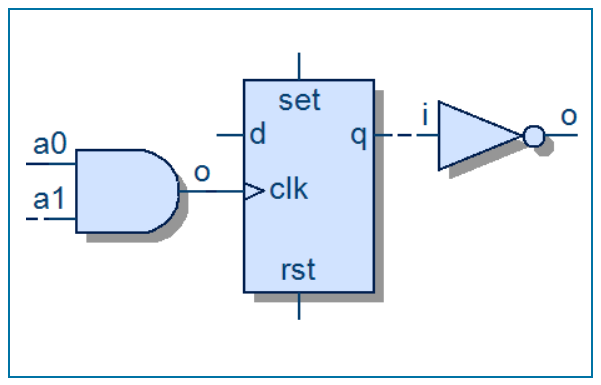

Semiconductor Development

Innovative electronic design debug, enhancing semiconductor quality and time-to-market.

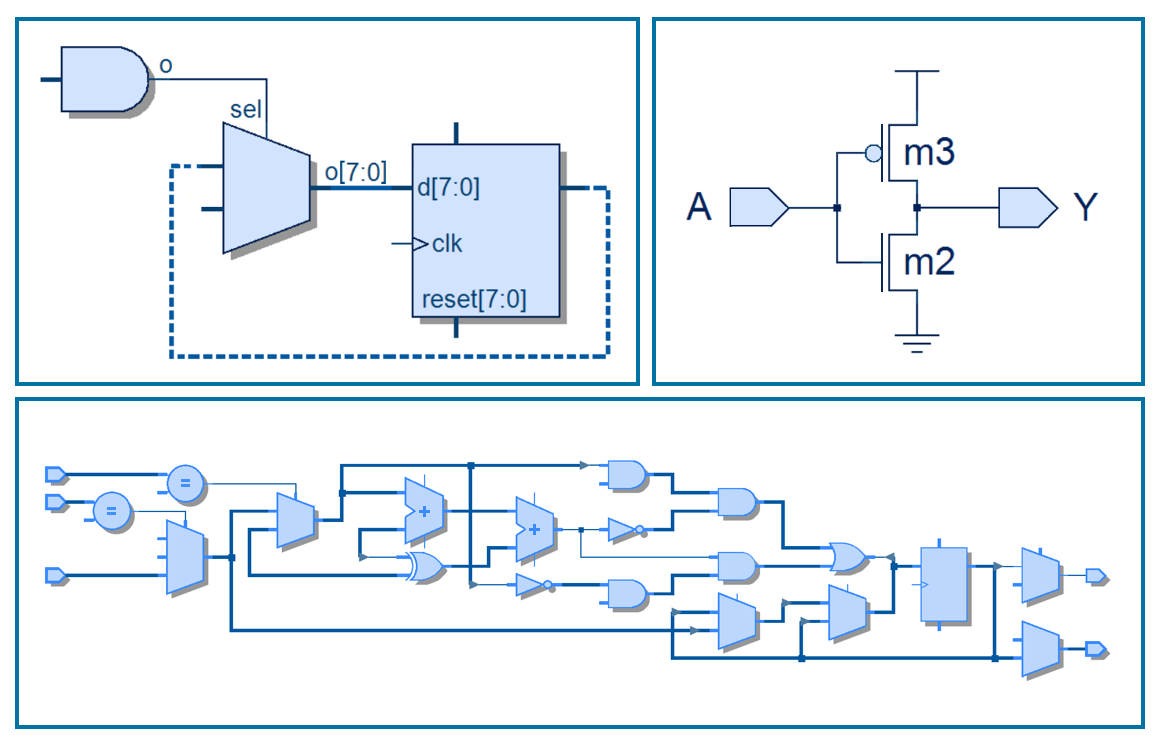

EDA & CAD Tool Development

Schematic generation and visualization libraries for accelerated EDA/CAD tool development.

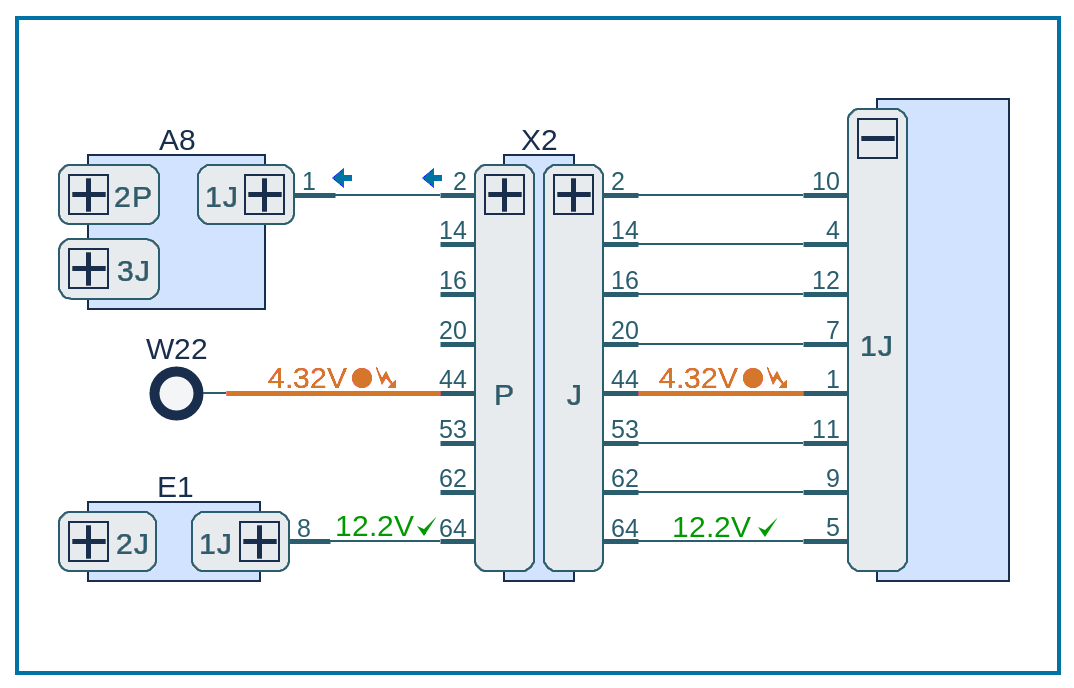

Automotive & Aerospace

Advanced electronic visualization for rapid & reliable development, manufacture and service.

Upcoming Events

We are looking forward to meeting you at:

What's New?

Our latest press releases and articles:

Altair Expands Electronic System Design Technology with Acquisition of Concept Engineering

TROY, Mich. – June 13, 2022 – Altair (Nasdaq: ALTR), a global leader in computational science and artificial intelligence (AI), acquired Concept Engineering, the leading provider of electronic system visualization software that accelerates the development, manufacture, and service of complex electrical and electronic systems.

Concept Engineering and Vtool Team Up to Deliver a Unique, Next-Generation Debug Solution

Freiburg, Germany – March 24, 2022 – Vtool Smart Verification and Concept Engineering today announced a partnership to deliver a unique EDA visualization solution for the semiconductor industry by connecting their advanced technologies Cogita™ and StarVision PRO™/RTLvision PRO™, creating a next-generation, unified Application Specific Integration Circuit (ASIC) and System on Chip (SoC) debug solution.

Concept Engineering Celebrates 30 Years of Innovation at DAC

Freiburg, Germany – July 20, 2020 – As part of its 30th anniversary, Concept Engineering, specialists in visualization and debugging technology for electronic circuits and electrical systems, will showcase its industry-leading visualization and debugging solutions at the virtual Design Automation Conference (DAC) Exhibition being held Monday, Tuesday, and Wednesday, July 20 – 22, 2020.

Concept Engineering Reveals EEvision Platform for On-board Electrical System Exploration at the 2020 WHMA Wire Harness Conference

Freiburg, Germany – February 11, 2020 – Concept Engineering, which specializes in visualization and debugging technologies for electronic circuits and systems, will showcase the company’s latest software solution, EEvision™ platform, at the Wire Harness Manufacturer’s Association (WHMA) Wire Harness Conference 2020, in Las Vegas, NV, February 18 – 20, 2020.

NASA-JPL adopts Concept Engineering’s E-engine and EEvision technologies to develop electronics for missions to Mars and Jupiter

Freiburg, Germany – May 24, 2019 – Concept Engineering, specialists in visualization in debugging technology for electronic circuits and systems, today announced that NASA’s Jet Propulsion Laboratory will use Concept Engineering’s E-engine™ and EEvision™ system visualization software to develop electronics for space missions to Mars and Jupiter moon Europa.