## StarVision<sup>®</sup> PRO: A Customizable Mixed-Signal Debugging Platform

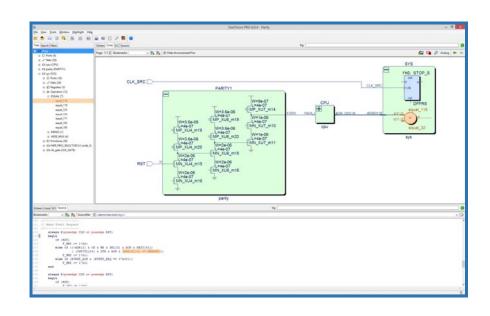

S tarVision PRO provides engineers with the ability to quickly and easily understand and debug mixedmode designs and to integrate IP building blocks into their complex SoCs and ICs.

**All-in-One** – Due to the increasing use of building blocks in SoC design, engineers need to work at different design levels (RTL, gate, transistor, analog, parasitic) as well as with different design languages and netlist formats. To support this challenge, Concept Engineering developed StarVision PRO, an integrated debugging cockpit for mixedsignal and digital design that makes analysis and debugging of complex SoC and IC designs easy and more transparent.

**Easy Design Exploration** – The interactive design navigation window shows schematic fragments of just the critical portion of the design while, at the same time, providing links to the original source code fragments (RTL, Netlist, SPICE) and to simulation results.

- Verilog-AMS, SystemVerilog, VHDL, SPICE, HSPICE<sup>®</sup>, Eldo<sup>®</sup>, Spectre<sup>®</sup>

- AMS viewer, RTL viewer, Netlist viewer and SPICE viewer in one tool

- Mixed-Signal Debugger Makes IP-based design more transparent

- 64-bit database handles today's largest SoCs and ASICs

- Integrated Waveform Viewer with source code link and schematic link

- Customizable netlist pruning (Verilog, SPICE, SPEF, DSPF)

- Advanced batch processing for automated tool flow

- Tcl based API for user-defined electrical rule checks and customization

**Verilog-AMS Support** – StarVision PRO reads Verilog-AMS designs and offers exciting options to explore and debug complex mixed-signal, SoC, IoT and RF integrated circuits.

**Clock Tree Extraction** – Clock signals are often a source of problems in complex SoC design. StarVision PRO automatically extracts and analyzes clock trees and gives an immediate view of clock trees and clock domains.

**Waveform Viewer and Signal Tracing** – StarVision PRO comes with a fully integrated waveform browser and with support for interactive signal tracing in the source code, schematic view and waveform window. StarVision PRO compiles VCD simulation data into its own high-speed format for accelerated waveform browsing and signal tracing.

**Path Extraction** – The customizable path extraction engine can automatically identify and extract critical paths in a design. These can be explored and cross-probed in different views to reduce both the complexity and time of the debug cycle.

**Automatic Logic Recognition** – The built-in automatic logic recognition engine creates digital logic schematics from pure SPICE-level netlists for easy design exploration.

Customization – Users can write API code to analyze the design and generate user-specific design reports and design rule checks.

**Improved Productivity** – Being able to analyze AMS-level, RTL-level, gate-level and transistor-level at the same time in just one debug cockpit increases design and verification engineers productivity, reducing product development time and debug cycle time.

## At a Glance

| FEATURE                                                            | BENEFITS                                                                                                                                                                                                 |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ultra fast HDL reader and graphics on the fly                      | Graphical representations make it easier to understand, debug, change and optimize Verilog, VHDL, SystemVerilog and Verilog-AMS code                                                                     |

| Schematics from SPICE netlists                                     | Schematics provide easier and faster debugging for complex circuits.<br>Supported dialects include SPICE, HSPICE <sup>®</sup> , Calibre <sup>®</sup> , CDL, Eldo <sup>®</sup> and Spectre <sup>®</sup> . |

| 64-bit database                                                    | Higher performance and increased capacity, for very large designs                                                                                                                                        |

| Powerful GUI                                                       | Multiple views, including tree, schematic, waveform and source file plus drag<br>and drop between different views for increased circuit understanding                                                    |

| Cone Window                                                        | Incremental schematic navigation for easy design exploration                                                                                                                                             |

| Tcl UserWare API                                                   | Allows interfacing with tool flow and definition of electrical rule checks                                                                                                                               |

| Circuit fragment save and netlist pruning                          | Circuit netlists can be exported for future reuse as IP, or for partial simulation (Verilog, SPICE, SPEF, DSPF)                                                                                          |

| Automatic clock tree and clock domain extraction and visualization | Faster detection and resolution of clock domain problems                                                                                                                                                 |

| Full support for mixed language and mixed-signal designs           | Designers can easily debug today's most complex heterogeneous designs<br>(Verilog-AMS, SystemVerilog, Verilog, VHDL, SPICE, HSPICE <sup>®</sup> , Spectre <sup>®</sup> )                                 |

| Parasitic analysis features                                        | Allows visualization and analysis of parasitic networks (SPEF, DSPF) and provides capabilities to export netlists for critical circuit fragments                                                         |

## **Company Contact**